07. 3-bit 4-to-1 MUX

| Owner | M. G. Sadek |

|---|---|

| Tags |

01 - Objective

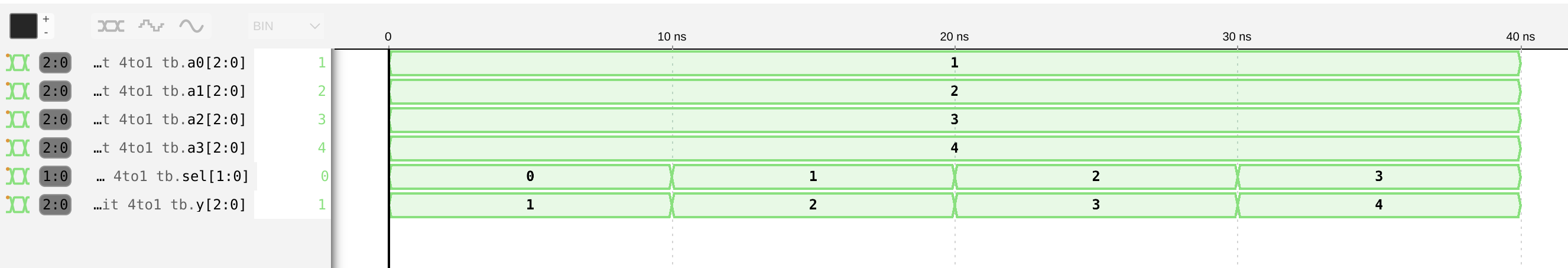

In this tutorial, we will discuss implementing a 3-bit 4-to-1 MUX.

The following code defines an entity called mux_4to1 with inputs a0, a1, a2, a3, and sel, and output y. The sel input selects which of the four inputs (a0, a1, a2, or a3) is passed through to the output y. The code uses a case statement to select the correct input based on the value of sel. The others => 'X' statement in the case statement assigns an undefined value to y if sel is not one of the defined values.

02. VHDL code for the 3-bit 4 to 1 multiplexer:

library ieee;

use ieee.std_logic_1164.all;

entity mux_3bit_4to1 is

port (

a0, a1, a2, a3 : in std_logic_vector(2 downto 0);

sel : in std_logic_vector(1 downto 0);

y : out std_logic_vector(2 downto 0)

);

end entity;

architecture behavioral of mux_3bit_4to1 is

begin

process (a0, a1, a2, a3, sel)

begin

case sel is

when "00" =>

y <= a0;

when "01" =>

y <= a1;

when "10" =>

y <= a2;

when others =>

y <= a3;

end case;

end process;

end architecture;03. Sample Testbench:

library ieee;

use ieee.std_logic_1164.all;

entity mux_3bit_4to1_tb is

end entity;

architecture behavioral of mux_3bit_4to1_tb is

signal a0, a1, a2, a3, y : std_logic_vector(2 downto 0);

signal sel : std_logic_vector(1 downto 0);

begin

uut: entity work.mux_3bit_4to1

port map (

a0 => a0,

a1 => a1,

a2 => a2,

a3 => a3,

sel => sel,

y => y

);

stimulus: process

begin

-- Test case 1: select input 0

sel <= "00";

a0 <= "001";

a1 <= "010";

a2 <= "011";

a3 <= "100";

wait for 10 ns;

assert y = "001" report "Test case 1 failed" severity error;

-- Test case 2: select input 1

sel <= "01";

a0 <= "001";

a1 <= "010";

a2 <= "011";

a3 <= "100";

wait for 10 ns;

assert y = "010" report "Test case 2 failed" severity error;

-- Test case 3: select input 2

sel <= "10";

a0 <= "001";

a1 <= "010";

a2 <= "011";

a3 <= "100";

wait for 10 ns;

assert y = "011" report "Test case 3 failed" severity error;

-- Test case 4: select input 3

sel <= "11";

a0 <= "001";

a1 <= "010";

a2 <= "011";

a3 <= "100";

wait for 10 ns;

assert y = "100" report "Test case 4 failed" severity error;

wait;

end process;

end architecture;04. Simulation Output