08. Processes [D-Flip-Flop]

| Owner | M. G. Sadek |

|---|---|

| Tags |

01 - Objective

In this tutorial, we will teach you about modelling processes in VHDL, this will be explained using D-Flip-Flops.

02 - Logic Gates Implementation

D-FlipFlop Symbol:

%20a5cdf2a201ba47c3a8f8f65e5840c09a/D-flip-flop-symbol.png)

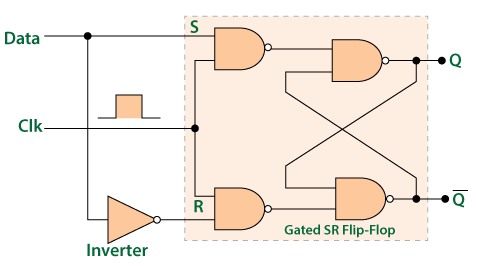

Circuit Diagram:

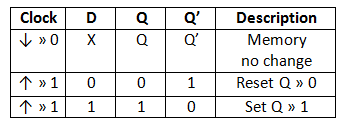

Truth Table:

VHDL code:

-- D flip-flop with asynchronous reset implementation

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity d_flipflop is

Port ( D : in STD_LOGIC;

clk : in STD_LOGIC;

reset : in STD_LOGIC;

Q : out STD_LOGIC;

Q_bar : out STD_LOGIC);

end d_flipflop;

architecture Behavioral of d_flipflop is

begin

process (reset, clk)

begin

if reset = '1' then

Q <= '0';

Q_bar <= '1';

elsif rising_edge(clk) then

Q <= D;

Q_bar <= not D;

end if;

end process;

end Behavioral;Sample Testbench

-- D flip-flop testbench definition

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity d_flipflop_tb is

end d_flipflop_tb;

architecture Behavioral of d_flipflop_tb is

component d_flipflop is

Port ( D : in STD_LOGIC;

clk : in STD_LOGIC;

reset : in STD_LOGIC;

Q : out STD_LOGIC;

Q_bar : out STD_LOGIC);

end component;

signal D, clk, reset, Q, Q_bar : std_logic;

begin

-- Instantiate the D flip-flop

dut: d_flipflop Port map (D => D, clk => clk, reset => reset, Q => Q, Q_bar => Q_bar);

-- Clock generation process

clk_proc: process

begin

clk <= '0';

wait for 5 ns;

while true loop

clk <= not clk;

wait for 5 ns;

end loop;

end process;

-- Stimulus process to test the flip-flop

stim_proc: process

begin

-- Reset the flip-flop

reset <= '1';

D <= '0';

wait for 10 ns;

reset <= '0';

wait for 10 ns;

-- Set D = 1

D <= '1';

wait for 10 ns;

assert (Q = '1' and Q_bar = '0')

report "Error: Q should be 1 and Q_bar should be 0" severity error;

-- Set D = 0

D <= '0';

wait for 10 ns;

assert (Q = '0' and Q_bar = '1')

report "Error: Q should be 0 and Q_bar should be 1" severity error;

-- Set D = 1 again

D <= '1';

wait for 10 ns;

assert (Q = '1' and Q_bar = '0')

report "Error: Q should be 1 and Q_bar should be 0" severity error;

-- Reset the flip-flop again

reset <= '1';

wait for 10 ns;

reset <= '0';

wait for 10 ns;

-- Set D = 0

D <= '0';

wait for 10 ns;

assert (Q = '0' and Q_bar = '1')

report "Error: Q should be 0 and Q_bar should be 1" severity error;

-- Set D = 1 again

D <= '1';

wait for 10 ns;

assert (Q = '1' and Q_bar = '0')

report "Error: Q should be 1 and Q_bar should be 0" severity error;

-- Wait for a few more clock cycles

wait for 20 ns;

-- Set D = 0 again

D <= '0';

wait for 10 ns;

assert (Q = '0' and Q_bar = '1')

report "Error: Q should be 1 and Q_bar should be 0" severity error;

-- Finish the simulation

wait;

end process;

end Behavioral;03 - Simulation Process

04 - Flashing Process

Please follow the same steps found in lab-03 in order to synthesise and flash the FPGA.

05 - Tasks

- Implement JK-FlipFlop

- Implement T-FlipFlop